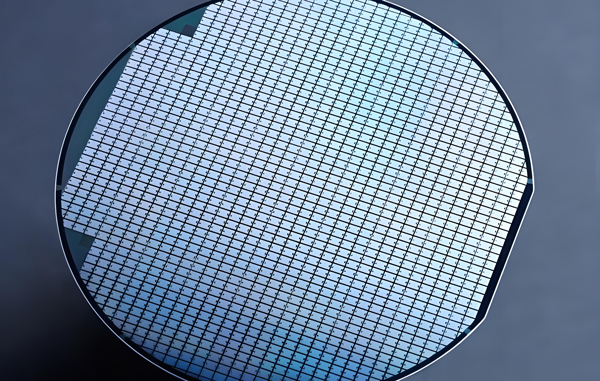

半导体薄膜工艺是芯片制造中不可或缺的基础环节,其本质是在晶圆表面精准沉积或生长纳米级薄膜,赋予芯片导电、绝缘或保护功能。这些薄膜的厚度通常在几埃到微米之间,却决定了晶体管的性能、互连的可靠性和器件的寿命。无论是逻辑芯片的栅极介质层,还是存储器的电容结构,亦或是功率半导体的钝化保护膜,薄膜工艺贯穿芯片制造的每个关键阶段。

主流技术路线与原理

化学气相沉积(CVD)

通过气态前驱体在高温或等离子体环境下的化学反应,在晶圆表面形成固态薄膜。例如,多晶硅、氮化硅和二氧化硅等材料均可通过CVD实现高质量沉积。

常压CVD(APCVD):适合厚膜生长,如外延硅层;

低压CVD(LPCVD):用于制备均匀的氮化硅掩膜层;

等离子体增强CVD(PECVD):能在低温下沉积介质层,减少对芯片的热损伤。

CVD的优势在于优异的台阶覆盖性,尤其适合复杂三维结构,但其反应气体管理和副产物控制是技术难点。

物理气相沉积(PVD)

通过物理手段(如溅射、蒸发)将靶材原子转移到晶圆表面。

磁控溅射:主流PVD技术,利用等离子体轰击金属靶材,溅射出的原子沉积成导电薄膜,广泛应用于铝、铜互连工艺;

电子束蒸发:通过高能电子束熔化靶材(如金、钛),形成高纯度薄膜。

PVD沉积速率快、纯度可控,但台阶覆盖率较差,需结合后续工艺优化。

原子层沉积(ALD)

通过交替通入不同前驱体,在表面发生自限制反应,逐层生长原子级均匀的薄膜。例如:

高k栅介质材料(如HfO?)和DRAM电容的Al?O?/TiO?叠层均依赖ALD技术。

ALD的厚度控制精度可达单原子层(±0.1nm),但沉积速度较慢、成本较高,通常仅用于关键功能层。

关键设备与技术挑战

CVD设备

热壁式CVD炉:用于批量生产多晶硅或氧化物,温度均匀性需控制在±2℃以内;

单片式PECVD设备:集成射频等离子体源,支持12英寸晶圆的低损伤沉积,但气体分配均匀性和等离子体稳定性是核心挑战。

PVD设备

磁控溅射设备:通过优化磁场分布提升靶材利用率至70%以上,但大尺寸铜靶的加工精度和低损伤溅射(避免晶体管性能退化)仍需突破;

离子化PVD(I-PVD):通过离子化靶材原子改善台阶覆盖率,已成为5nm以下先进制程的标配技术。

ALD设备

热ALD与等离子体ALD:前者在200~350℃下生成致密薄膜,后者支持低温沉积(<100℃)以兼容敏感材料;

空间ALD技术:通过晶圆与喷头的相对运动提升沉积速度,例如ASM的Pulsar?系统已实现量产应用。

应用场景与典型案例

逻辑芯片:高k金属栅结构依赖ALD沉积的HfO?和PVD制备的TiN薄膜;铜互连工艺需结合PVD的TaN阻挡层与CVD的铜种子层。

DRAM电容:通过ALD交替堆叠Al?O?和TiO?,实现高密度电荷存储。

功率半导体:PECVD生长的Si?N?钝化层可防止湿气侵蚀IGBT芯片表面。

先进封装:重布线层(RDL)和硅通孔(TSV)集成聚酰亚胺介电层与铜导线。

国内外差距与突围路径

设备性能:国际领先企业的ALD设备已实现300mm晶圆±1%的厚度均匀性,而国产设备在200mm晶圆上的均匀性仍为±3%;

材料与部件:PVD靶材利用率方面,国产铜靶的利用率仅50%~60%,低于国际水平的75%;高纯度前驱体材料(如WF?、HfCl?)和真空泵等核心部件仍依赖进口;

工艺集成:台积电3nm工艺采用ALD HfZrO?栅介质,而国内28nm工艺仍以传统CVD为主。

突破方向:

攻克高纯度石英管、靶材和前驱体的国产化;

开发AI驱动的工艺控制系统,提升薄膜均匀性;

布局宽禁带半导体(如GaN、SiC)的外延与集成技术。

未来趋势:精准化与多维拓展

原子级精度制造:二维材料(如MoS?)的单层沉积、亚纳米界面控制技术将推动新型器件诞生;

宽禁带半导体:氮化镓外延层(MOCVD)和氧化镓沟道层(HVPE)需求增长,驱动专用设备研发;

绿色制造:替代高毒性前驱体(如用有机钨化合物替代WF?),并强化尾气回收;

智能化:通过机器学习实时优化沉积参数,将工艺稳定性提升20%以上。

结语

半导体薄膜工艺是连接材料科学与芯片性能的桥梁。从CVD的化学反应到ALD的原子级操控,每一层薄膜的沉积都是对精度与效率的极致追求。突破设备、材料和工艺的协同瓶颈,将成为中国半导体产业攀登技术高峰的关键战役。